सोप 8 बॉडी मार्किंग। चिप पैकेज के प्रकार

वर्तमान में, दुनिया भर में सभी प्रकार के कार्यों के साथ अविश्वसनीय संख्या में माइक्रो सर्किट का उत्पादन किया जा रहा है। दर्जनों निर्माताओं के हजारों अलग-अलग चिप्स हैं। लेकिन यह स्पष्ट है कि चिप पैकेजों के एक निश्चित मानकीकरण की आवश्यकता है ताकि डेवलपर्स अंतिम इलेक्ट्रॉनिक उपकरणों (टीवी, टेप रिकॉर्डर, कंप्यूटर इत्यादि) में स्थापित मुद्रित सर्किट बोर्डों के निर्माण के लिए आसानी से उनका उपयोग कर सकें। इसलिए, समय के साथ, माइक्रोक्रिकिट फॉर्म कारकों का गठन किया गया, जिसके लिए सभी विश्व निर्माता अनुकूलन करते हैं। उन सभी का वर्णन करना कठिन है, लेकिन यह आवश्यक नहीं है, क्योंकि उनमें से कुछ विशिष्ट कार्यों के लिए डिज़ाइन किए गए हैं जिनका सामना आपको कभी नहीं करना पड़ेगा।

इसलिए, नीचे केवल सबसे आम और लोकप्रिय ज्ञात प्रकार के बाड़े हैं जिन्हें आप दुकानों में पा सकते हैं और अपनी परियोजनाओं में उपयोग कर सकते हैं।

1 . आवास प्रकार डीआईपी

संक्षिप्त नाम डीआईपी का मतलब डुअल इन-लाइन पैकेज है, जिसका अर्थ है "दो लाइनों का पैकेज।" इस प्रकार में एक आयताकार आकार होता है जिसमें संपर्कों (पैरों) की दो पंक्तियाँ होती हैं जो केस के लंबे किनारों की ओर निर्देशित होती हैं।

इस प्रकार का पैकेज 1965 में सामने आया और कुछ पहले व्यावसायिक रूप से उत्पादित माइक्रो-सर्किट के लिए मानक बन गया। यह 1970 और 1980 के दशक में इलेक्ट्रॉनिक्स उद्योग में सबसे लोकप्रिय था। यह मामला स्वचालित असेंबली और विकास बोर्ड स्थापना के लिए उपयुक्त है।

एक तरफ आसन्न पैरों की धुरी के बीच की दूरी 2.54 मिमी है, जो ब्रेडबोर्ड संपर्कों की पिच से मेल खाती है। इसलिए, इस प्रकार के माइक्रोसर्किट का उपयोग इवोल्वेक्टर निर्माण किट में किया जाता है। इसे वर्तमान में अप्रचलित माना जाता है। पीसीबी उद्योग में इसे धीरे-धीरे पीएलसीसी और एसओआईसी जैसे सतह माउंट पैकेजों द्वारा प्रतिस्थापित किया गया है।

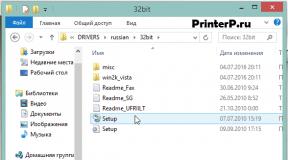

2. SOIC पैकेज प्रकार

SOIC का मतलब स्मॉल-आउटलाइन इंटीग्रेटेड सर्किट है। इस प्रकार के पैकेज वाले चिप्स केवल मुद्रित सर्किट बोर्ड पर सतह पर लगाने के लिए होते हैं और वास्तव में डीआईपी पैकेज प्रकार की तुलना में आकार में बहुत छोटे होते हैं। इस प्रकार के केस में एक आयत का आकार होता है जिसके लंबे किनारों पर पिन की दो पंक्तियाँ होती हैं। पैरों के बीच की दूरी 1.27 मिमी है, केस की ऊंचाई डीआईपी केस की तुलना में 3 गुना कम है और 1.75 मिमी से अधिक नहीं है। एसओआईसी पैकेज में माइक्रो सर्किट डीआईपी पैकेज में उनके समकक्षों की तुलना में 30-50% कम मुद्रित सर्किट बोर्ड क्षेत्र पर कब्जा करते हैं, यही कारण है कि वे आज भी व्यापक रूप से उपयोग किए जाते हैं। बोर्ड की सतह पर आसानी से टांका लगाने के लिए पैरों के सिरे मोड़े हुए हैं। उपकरणों के त्वरित प्रोटोटाइप के लिए ब्रेडबोर्ड में इस प्रकार की चिप स्थापित करना असंभव है।

आमतौर पर, डीआईपी और एसओआईसी पैकेज में समान माइक्रो सर्किट के पिन की संख्या समान होती है। इस प्रकार के माइक्रोक्रिकिट को नामित करने के लिए, न केवल संक्षिप्त नाम SOIC का उपयोग किया जा सकता है, बल्कि पिन की संख्या के बाद SO अक्षर का भी उपयोग किया जा सकता है। उदाहरण के लिए, यदि चिप में 16 पिन हैं, तो इसे SOIC-16 या SO-16 नामित किया जा सकता है।

आवासों की अलग-अलग चौड़ाई हो सकती है। सबसे सामान्य आकार 0.15 हैं; 0.208 और 0.3 इंच. सोल्डरिंग सीखने के लिए इन माइक्रो-सर्किट का उपयोग अतिरिक्त "इवोल्वेक्टर" किट में करना संभव है।

3.पीएलसीसी आवास प्रकार

पीएलसीसी - प्लास्टिक लीडेड चिप कैरियर के लिए खड़ा है - प्लास्टिक लीडेड चिप धारक। प्रकार एक वर्गाकार आवास है जिसके संपर्क चार तरफ स्थित हैं। संपर्कों के बीच की दूरी 1.27 मिमी है। यह आवास एक विशेष पैनल में स्थापना के लिए डिज़ाइन किया गया है। डीआईपी पैकेज की तरह, यह वर्तमान में बहुत व्यापक नहीं है। पर्सनल कंप्यूटर या अन्य कंप्यूटिंग सिस्टम में मदरबोर्ड पर BIOS चिप्स के रूप में उपयोग की जाने वाली फ्लैश मेमोरी चिप्स का उत्पादन करने के लिए इसका उपयोग किया जा सकता है।

4. केस प्रकार TO-92

TO-92 - ट्रांजिस्टर आउटलाइन पैकेज, केस स्टाइल 92 के लिए खड़ा है - डिजिटल पदनाम 92 के तहत संशोधन के साथ ट्रांजिस्टर के लिए एक केस के रूप में। जैसा कि नाम से पता चलता है, इस प्रकार के केस का उपयोग ट्रांजिस्टर के लिए किया जाता है। यह कम-शक्ति ट्रांजिस्टर और अन्य तीन-टर्मिनल अर्धचालक इलेक्ट्रॉनिक घटकों का उत्पादन करता है, जिसमें एकीकृत वोल्टेज नियामक जैसे सरल चिप्स शामिल हैं। केस आकार में छोटा है, जैसा कि इवोल्वेक्टर निर्माण सेट से द्विध्रुवी ट्रांजिस्टर उठाकर देखा जा सकता है। वास्तव में, यह मामला एक साथ चिपके हुए दो प्लास्टिक हिस्सों का है, जिनके बीच एक फिल्म पर एक अर्धचालक घटक संलग्न है। शरीर के एक तरफ एक सपाट भाग होता है जिस पर निशान लगाए जाते हैं।

केस से तीन पिन (पैर) निकलते हैं, जिनके बीच की दूरी 1.15 से 1.39 मिमी तक हो सकती है। ऐसे आवास में निर्मित घटक 5 ए तक की धारा और 600 वी तक के वोल्टेज को पारित कर सकते हैं, लेकिन उनके छोटे आकार और गर्मी अपव्यय तत्व की अनुपस्थिति के कारण, उन्हें 0.6 डब्ल्यू तक की नगण्य शक्ति के लिए डिज़ाइन किया गया है।

5. केस प्रकार TO-220

इस प्रकार का पतवार TO-92 का रिश्तेदार है। अंतर डिज़ाइन में निहित है, जो TO-92 फॉर्म फैक्टर द्वारा प्रदान की जाने वाली उच्च शक्ति के घटकों और चिप्स पर केंद्रित है। TO-220 पैकेज ट्रांजिस्टर, एकीकृत वोल्टेज स्टेबलाइजर्स या रेक्टिफायर के लिए भी डिज़ाइन किया गया है। TO-220 केस पहले से ही मेटल हीट-सिंकिंग प्लेट (जिसे बेस कहा जाता है) की उपस्थिति के कारण 50 W तक की शक्ति के लिए डिज़ाइन किया गया है, जिसमें सेमीकंडक्टर डिवाइस क्रिस्टल, लीड और एक सीलबंद प्लास्टिक केस मिलाया जाता है।

सामान्य "ट्रांजिस्टर" TO-220 में तीन टर्मिनल होते हैं, लेकिन दो, चार, पांच और अधिक टर्मिनलों के साथ संशोधन भी होते हैं। पिन अक्षों के बीच की दूरी 2.54 मिमी है। अतिरिक्त कूलिंग रेडिएटर्स को माउंट करने के लिए बेस में ∅4.2 मिमी का छेद है। बेहतर गर्मी अपव्यय गुणों के कारण, इस आवास में इलेक्ट्रॉनिक घटक 70 ए तक की धाराएं पारित कर सकते हैं।

6. आवास प्रकार टीएसएसओपी

संक्षिप्त नाम TSSOP का मतलब थिन स्केल स्मॉल-आउटलाइन पैकेज है। इस प्रकार के आवास का उपयोग विशेष रूप से मुद्रित सर्किट बोर्डों पर सतह पर लगाने के लिए किया जाता है। इसकी मोटाई बहुत छोटी है, 1.1 मिमी से अधिक नहीं, और माइक्रोक्रिकिट के पिनों के बीच बहुत छोटी दूरी है - 0.65 मिमी।

इन हाउसिंग का उपयोग पर्सनल कंप्यूटर के लिए रैम चिप्स के निर्माण के साथ-साथ फ्लैश मेमोरी चिप्स के लिए भी किया जाता है। उनकी कॉम्पैक्टनेस के बावजूद, घटक घनत्व के लिए लगातार बढ़ती आवश्यकताओं के कारण कई आधुनिक उपकरणों में उन्हें अधिक कॉम्पैक्ट बीजीए-प्रकार पैकेजों द्वारा प्रतिस्थापित किया जा रहा है।

7.क्यूएफपी आवास प्रकार

संक्षिप्त नाम QFP क्वाड फ्लैट पैकेज के लिए है - एक वर्गाकार फ्लैट पैकेज। चिप पैकेजों का क्यूएफपी वर्ग पैकेजों का एक परिवार है जिसमें प्लेनर पिन होते हैं जो चारों तरफ समान दूरी पर होते हैं। ऐसे पैकेजों में माइक्रो सर्किट केवल सतह पर लगाने के लिए होते हैं। विभिन्न चिपसेट, माइक्रोकंट्रोलर और प्रोसेसर के उत्पादन के लिए यह आज सबसे लोकप्रिय प्रकार का आवास है। जब आप इवॉल्वेक्टर कंस्ट्रक्टर के दूसरे और तीसरे स्तर पर जाते हैं तो आप इसे सत्यापित कर सकते हैं। इन डिज़ाइनरों के नियंत्रक और सिंगल-बोर्ड कंप्यूटर ऐसे ही मामलों में प्रोसेसर और माइक्रोकंट्रोलर से लैस होते हैं।

कक्षा में क्यूएफपीकई उपवर्ग हैं:

. बीक्यूएफपी: अंग्रेज़ी से बम्पर्ड क्वाड फ्लैट पैकेज

. सीक्यूएफपी: अंग्रेज़ी से सिरेमिक क्वाड फ्लैट पैकेज

. मुख्यालयएफपी: अंग्रेज़ी से हीट सिंक्ड क्वाड फ्लैट पैकेज

.एलक्यूएफपी: अंग्रेज़ी से लो प्रोफाइल क्वाड फ्लैट पैकेज

. एसक्यूएफपी: अंग्रेज़ी से छोटा क्वाड फ्लैट पैकेज

.टीक्यूएफपी: अंग्रेज़ी से पतला क्वाड फ्लैट पैकेज

.वीक्यूएफपी: अंग्रेज़ी से बहुत छोटा क्वाड फ्लैट पैकेज

लेकिन उपवर्ग की परवाह किए बिना, "वर्गता" और संपर्कों के समान वितरण का सिद्धांत समान रहता है। किस्में केवल सामग्री, गर्मी अपव्यय क्षमता और आवास विन्यास के साथ-साथ आकार और आउटपुट के बीच की दूरी में भिन्न होती हैं। यह 0.4 से 1.0 मिमी तक होता है। QFP पैकेज में माइक्रो सर्किट के लिए पिन की संख्या आमतौर पर 200 से अधिक नहीं होती है।

इस लेख में हम सबसे बुनियादी चिप पैकेजों को देखेंगे जो रोजमर्रा के इलेक्ट्रॉनिक्स में अक्सर उपयोग किए जाते हैं।

डुबोना(अंग्रेज़ी) डी ual मैंएन-लाइन पीएककेज)-माइक्रोक्रिकिट के लंबे किनारों पर पिन की दो पंक्तियों वाला एक पैकेज। पहले, और शायद अब भी, डीआईपी पैकेज मल्टी-पिन माइक्रोसर्किट के लिए सबसे लोकप्रिय पैकेज था। यह इस तरह दिख रहा है:

माइक्रो सर्किट के पिनों की संख्या के आधार पर, "DIP" शब्द के बाद उसके पिनों की संख्या रखी जाती है। उदाहरण के लिए, एक माइक्रोसर्किट, या अधिक सटीक रूप से, एक atmega8 माइक्रोकंट्रोलर में 28 पिन होते हैं:

इसलिए, इसके आवास को DIP28 कहा जाएगा।

लेकिन इस माइक्रो सर्किट की हाउसिंग को DIP16 कहा जाएगा।

मूल रूप से, सोवियत संघ में डीआईपी पैकेज में लॉजिक चिप्स, ऑपरेशनल एम्पलीफायर आदि का उत्पादन किया गया था। आजकल, डीआईपी पैकेज भी अपनी प्रासंगिकता नहीं खोता है और इसमें अभी भी विभिन्न माइक्रो-सर्किट बनाए जाते हैं, जिनमें साधारण एनालॉग से लेकर माइक्रोकंट्रोलर तक शामिल हैं।

डीआईपी आवास प्लास्टिक से बना हो सकता है (जो कि ज्यादातर मामलों में होता है) और इसे कहा जाता है पीडीआईपी, साथ ही चीनी मिट्टी से - सीडीआईपी. शरीर का एहसास सीडीआईपीचट्टान की तरह कठोर, जो आश्चर्य की बात नहीं है क्योंकि यह सिरेमिक से बना है।

उदाहरण सीडीआईपीआवास.

वे भी हैं संशोधनोंएचडीआईपी, एसडीआईपी।

एचडीआईपी (एचखाना-बर्बाद करना डुबोना ) - गर्मी नष्ट करने वाला डीआईपी। ऐसे माइक्रो-सर्किट अपने माध्यम से एक बड़ा करंट प्रवाहित करते हैं, इसलिए वे बहुत गर्म हो जाते हैं। अतिरिक्त गर्मी को हटाने के लिए, ऐसे माइक्रोक्रिकिट में रेडिएटर या कुछ इसी तरह का होना चाहिए, उदाहरण के लिए, जैसे यहां माइक्रोचिप के बीच में दो रेडिएटर पंख हैं:

एसडीआईपी (एसमॉल डुबोना ) - छोटा डीआईपी। माइक्रो-सर्किट एक डीआईपी पैकेज में है, लेकिन माइक्रो-सर्किट के पैरों के बीच थोड़ी दूरी है:

एसआईपी मामला

एसआईपीचौखटा ( एसचिमनी मैंएन लाइन पी ackage) - एक तरफ लीड वाला एक फ्लैट केस। स्थापित करना बहुत आसान है और कम जगह लेता है। केस के नाम के बाद पिन की संख्या भी लिखी होती है। उदाहरण के लिए, SIP8 हाउसिंग में नीचे से एक मिक्रूहा।

यू एसआईपीसंशोधन भी हैं - ये हैं एचएसआईपी(एचखाना-बर्बाद करना एसआईपी). यानी वही मामला, लेकिन रेडिएटर के साथ

ज़िप आवास

ज़िप ( जेड igzag मैंएन लाइन पी ackage) - ज़िगज़ैग पैटर्न में व्यवस्थित लीड वाला एक सपाट केस। नीचे दी गई तस्वीर ZIP6 हाउसिंग दिखाती है। संख्या पिनों की संख्या है:

खैर, रेडिएटर वाला एक मामला एचज़िप:

हमने अभी मुख्य वर्ग को देखा है इन लाइन पैकेजमाइक्रो सर्किट ये चिप्स एक मुद्रित सर्किट बोर्ड में छेद-थ्रू माउंटिंग के लिए डिज़ाइन किए गए हैं।

उदाहरण के लिए, एक मुद्रित सर्किट बोर्ड पर स्थापित DIP14 चिप

और इसके निष्कर्ष बोर्ड के पीछे की तरफ, पहले से ही सोल्डर के बिना।

कोई अभी भी डीआईपी चिप्स को सरफेस-माउंट चिप्स (नीचे उन पर अधिक) की तरह सोल्डर करने, पिनों को 90 डिग्री के कोण पर मोड़ने, या उन्हें पूरी तरह से सीधा करने का प्रबंधन करता है। यह एक विकृति है), लेकिन यह काम करता है)।

आइए माइक्रो-सर्किट के दूसरे वर्ग पर चलते हैं - सतह माउंट चिप्सया तथाकथित एसएमडी घटक. उन्हें भी बुलाया जाता है तलीयरेडियो घटक.

ऐसे माइक्रो-सर्किट को मुद्रित सर्किट बोर्ड की सतह पर उनके लिए आवंटित मुद्रित कंडक्टरों के तहत टांका लगाया जाता है। क्या आपको एक पंक्ति में आयताकार पथ दिखाई देते हैं? ये मुद्रित कंडक्टर या लोकप्रिय हैं थूथन. यह बिल्कुल वही है जिस पर प्लेनर माइक्रो सर्किट को सोल्डर किया जाता है।

एसओआईसी पैकेज

माइक्रो-सर्किट के इस वर्ग का सबसे बड़ा प्रतिनिधि पैकेज्ड माइक्रो-सर्किट हैं SOIC (एसमॉल- हेरूपरेखा मैंएकीकृत सी ircuit) लंबे किनारों पर पिन वाला एक छोटा माइक्रोक्रिकिट है। यह काफी हद तक डीआईपी के समान है, लेकिन इसके निष्कर्षों पर ध्यान दें। वे शरीर की सतह के ही समानांतर हैं:

इस प्रकार उन्हें बोर्ड पर टांका लगाया जाता है:

खैर, हमेशा की तरह, "SOIC" के बाद की संख्या इस माइक्रोक्रिकिट के पिन की संख्या को इंगित करती है। ऊपर दी गई तस्वीर SOIC16 पैकेज में माइक्रोसर्किट दिखाती है।

शराबी (एसमॉल हेरूपरेखा पी ackage) - SOIC के समान।

एसओपी आवास संशोधन:

पीएसओपी- प्लास्टिक हाउसिंग एसओपी। बहुधा इसी का प्रयोग किया जाता है।

एचएसओपी- गर्मी नष्ट करने वाला एसओपी। बीच में छोटे रेडिएटर्स गर्मी दूर करने का काम करते हैं।

एसएसओपी(एसहंक एसमॉल हेरूपरेखा पीएककेज)- "झुर्रीदार" एसओपी। यानी एसओपी हाउसिंग से भी छोटा

टीएसएसओपी(टीहिन एसहंक एसमॉल हेरूपरेखा पीएककेज)- पतला एसएसओपी। वही एसएसओपी, लेकिन रोलिंग पिन से "स्मीयर"। इसकी मोटाई SSOP से कम है. मूल रूप से, माइक्रो सर्किट TSSOP पैकेज में बनाए जाते हैं, जो काफी गर्म होते हैं। इसलिए, ऐसे माइक्रो-सर्किट का क्षेत्र पारंपरिक माइक्रो-सर्किट की तुलना में बड़ा होता है। संक्षेप में, एक रेडिएटर आवास)।

SOJ- वही एसओपी, लेकिन पैर एक अक्षर के आकार में मुड़े हुए हैं "जे"माइक्रोक्रिकिट के नीचे ही। इन्हीं पैरों के नाम पर एसओ बॉडी का नाम रखा गया जे:

खैर, हमेशा की तरह, पिन की संख्या पैकेज प्रकार के बाद इंगित की जाती है, उदाहरण के लिए SOIC16, SSOP28, TSSOP48, आदि।

क्यूएफपी पैकेज

क्यूएफपी (क्यूउड एफअक्षां पीएककेज)-चतुष्कोणीय सपाट शरीर। इसके साथी SOIC से मुख्य अंतर यह है कि पिन ऐसी चिप के सभी तरफ स्थित होते हैं

संशोधन:

पीक्यूएफपी- क्यूएफपी प्लास्टिक आवास। सीक्यूएफपी- क्यूएफपी सिरेमिक आवास। मुख्यालयएफपी- क्यूएफपी ताप नष्ट करने वाला आवास।

टीक्यूएफपी (टीहिन क्यूउड एफअक्षां पीएके)- पतला क्यूएफपी पैकेज। इसकी मोटाई इसके क्यूएफपी चचेरे भाई की तुलना में बहुत पतली है

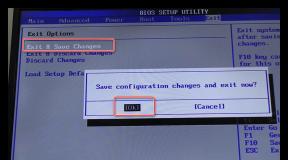

पीएलसीसी (पीलास्टिक एलईडेड सीकूल्हा सीवाहक)और सीएलसीसी (सीइरामिक एलईडेड सीकूल्हा सीवाहक)- क्रमशः एक प्लास्टिक और सिरेमिक केस, किनारों पर स्थित संपर्कों के साथ, एक विशेष सॉकेट में स्थापना के लिए, जिसे लोकप्रिय रूप से "पालना" कहा जाता है। एक विशिष्ट उदाहरण आपके कंप्यूटर में BIOS चिप है।

ऐसे माइक्रो-सर्किट के लिए "बिस्तर" इस तरह दिखता है:

और इस तरह माइक्रोक्रिकिट पालने में "झूठ" बोलता है।

कभी-कभी ऐसे माइक्रो-सर्किट भी कहलाते हैं क्यूएफजे, जैसा कि आपने अनुमान लगाया होगा, अक्षर के आकार के पिन के कारण "जे"

खैर, पिन की संख्या केस के नाम के बाद रखी गई है, उदाहरण के लिए PLCC32।

पीजीए पैकेज

पी.जी.ए. (पीमें जीछुटकारा दिलाना एरे)- पिन पिन का एक मैट्रिक्स। यह एक आयताकार या चौकोर केस होता है, जिसके निचले हिस्से में पिन लगे होते हैं।

ऐसे माइक्रो-सर्किट विशेष क्रिब में भी स्थापित किए जाते हैं, जो एक विशेष लीवर का उपयोग करके माइक्रो-सर्किट के टर्मिनलों को जकड़ते हैं।

पीजीए पैकेज का उपयोग मुख्य रूप से आपके पर्सनल कंप्यूटर के लिए प्रोसेसर बनाने के लिए किया जाता है।

एलजीए मामला

एलजीए (एलऔर जीछुटकारा दिलाना एरे) - संपर्क पैड के मैट्रिक्स के साथ एक प्रकार का माइक्रोक्रिकिट पैकेज। प्रोसेसर के लिए कंप्यूटर प्रौद्योगिकी में सबसे अधिक उपयोग किया जाता है।

एलजीए चिप्स के लिए पालना कुछ इस तरह दिखता है:

यदि आप बारीकी से देखें, तो आप स्प्रिंग-लोडेड संपर्क देख सकते हैं।

चिप में ही, इस मामले में पीसी प्रोसेसर में, बस धातुकृत पैड होते हैं:

हर चीज़ को काम करने के लिए, एक शर्त पूरी करनी होगी: माइक्रोप्रोसेसर को पालने पर कसकर दबाया जाना चाहिए। इसके लिए विभिन्न प्रकार की कुंडी का उपयोग किया जाता है।

बीजीए पैकेज

बीजीए (बीसभी जीछुटकारा दिलाना एरे) - गेंदों का एक मैट्रिक्स।

जैसा कि हम देख सकते हैं, यहां पिनों को सोल्डर बॉल्स से बदल दिया गया है। ऐसी एक चिप सैकड़ों सीसे की गेंदों को समायोजित कर सकती है। बोर्ड की जगह की बचत शानदार है। इसलिए, बीजीए हाउसिंग में माइक्रोसर्किट का उपयोग मोबाइल फोन, टैबलेट, लैपटॉप और अन्य माइक्रोइलेक्ट्रॉनिक उपकरणों के उत्पादन में किया जाता है। मैंने सोल्डरिंग बीजीए चिप्स लेख में बीजीए को पुनः सोल्डर करने के तरीके के बारे में भी लिखा है।

लाल वर्गों में मैंने मोबाइल फोन बोर्ड पर बीजीए पैकेज में माइक्रोसर्किट को चिह्नित किया। जैसा कि आप देख सकते हैं, अब सभी माइक्रोइलेक्ट्रॉनिक्स BGA चिप्स पर बने हैं।

बीजीए प्रौद्योगिकी माइक्रोइलेक्ट्रॉनिक्स का शिखर है। वर्तमान में, दुनिया माइक्रोबीजीए पैकेज तकनीक पर स्विच कर चुकी है, जहां गेंदों के बीच की दूरी और भी छोटी है, और आप एक चिप के नीचे हजारों (!) पिन भी फिट कर सकते हैं!

इसलिए हमने माइक्रो-सर्किट के मुख्य आवासों को अलग कर दिया है।

एसओआईसी पैकेज एसओपी में चिप को कॉल करने या एसओपी एसएसओपी को कॉल करने में कुछ भी गलत नहीं है। QFP मामले को TQFP कहने में भी कुछ गलत नहीं है। उनके बीच की सीमाएँ धुंधली हैं और ये केवल परंपराएँ हैं। लेकिन यदि आप BGA पैकेज DIP में एक माइक्रोसर्किट कहते हैं, तो यह पूरी तरह से विफल हो जाएगा।

शुरुआती रेडियो शौकीनों को माइक्रो-सर्किट के लिए तीन सबसे महत्वपूर्ण पैकेजों को याद रखना चाहिए - ये हैं डीआईपी, एसओआईसी (एसओपी) और क्यूएफपी बिना किसी संशोधन के और यह उनके अंतर को जानने के लायक भी है। मूल रूप से, यह इस प्रकार के माइक्रोक्रिकिट हाउसिंग हैं जिनका उपयोग रेडियो शौकिया अपने अभ्यास में सबसे अधिक बार करते हैं।

इस समय तक, कुछ घटकों (प्रतिरोधकों, कैपेसिटर) को पहले ही विकसित और महारत हासिल किया जा चुका था, जिनका उपयोग जीआईएस और एसएमई के निर्माण में किया गया था। हालाँकि, टीएमपी ने जलवायु कारकों के प्रतिरोध की आवश्यकताओं को कड़ा कर दिया, क्योंकि जीआईएस और एसएमई के लिए चिप प्रतिरोधक और कैपेसिटर जीआईएस मामलों के अंदर उपयोग के लिए असुरक्षित डिजाइन में निर्मित किए गए थे।

वर्तमान में, टीएमपी के लिए घटकों की एक विस्तृत श्रृंखला विकसित की गई है, जिसमें प्रतिरोधक, कैपेसिटर (परिवर्तनीय वाले सहित), इंडक्टर्स, माइक्रोट्रांसफॉर्मर, रिले, क्वार्ट्ज रेज़ोनेटर, डायोड, ट्रांजिस्टर, माइक्रोसर्किट, माइक्रोस्विच इत्यादि शामिल हैं। इन घटकों में कई प्रकार के आवास हैं: टिनयुक्त सिरों के साथ सीसा रहित, छोटे गल पंख या जे-आकार के सीसे के साथ, धातुयुक्त सिरों के साथ बेलनाकार आवास। आइए इन मामलों पर करीब से नज़र डालें।

चिप बॉडी -प्रतिरोधक, जम्पर और कैपेसिटर जैसे सरल निष्क्रिय घटकों के लिए सीसा रहित आयताकार पैकेज (चित्र 2.1)।

चित्र 2.1 - सरल चिप घटकों के आवास

चिप रेसिस्टर्स और चिप कैपेसिटर का निर्माण समूह प्रौद्योगिकी का उपयोग करके बड़े आकार के सब्सट्रेट्स (आमतौर पर 60x48 मिमी) पर किया जाता है, फिर सब्सट्रेट को स्क्रिब करने के बाद अलग-अलग हिस्सों में तोड़ दिया जाता है (अंग्रेजी शब्द चिप का अर्थ टुकड़ा होता है)। तोड़ने के बाद, प्रत्येक छोर के लिए तीन या पांच तरफ चिप घटक के सिरों पर एक बहुपरत धातुकरण (मोटी फिल्म कंडक्टर - निकल बाधा परत - सोल्डर परत) लगाया जाता है (बाद वाला विकल्प अत्यधिक विश्वसनीय घटकों के लिए उपयोग किया जाता है)। चिप प्रतिरोधकों के निर्माण में आमतौर पर मोटी फिल्म तकनीक का उपयोग किया जाता है। मोटी फिल्म चिप अवरोधक का एक विशिष्ट डिज़ाइन चित्र 2.2 में दिखाया गया है। रोकनेवाला में एक सिरेमिक बेस (ए 1 2 ओ 3 सब्सट्रेट), एक प्रतिरोधक परत (रूथेनियम ऑक्साइड), एक आंतरिक संपर्क परत (पैलेडियम-सिल्वर), एक मध्यवर्ती निकल बाधा परत और एक बाहरी संपर्क परत (टिन-लेड मिश्र धातु) शामिल है। . अवरोधक बॉडी को मूल्य के अमिट कोड अंकन के साथ बोरोसिलिकेट ग्लास कोटिंग द्वारा संरक्षित किया जाता है।

चित्र 2.2 - एक मोटी फिल्म चिप अवरोधक का डिज़ाइन

प्रतिरोधों के अंकन में सरल के लिए तीन अंक और उच्च-सटीक प्रतिरोधों के लिए चार अंक होते हैं, अंतिम अंक शून्य की संख्या को दर्शाता है जिसे ओम मान के दाईं ओर जोड़ा जाना चाहिए। उदाहरण के लिए: 160-16 ओम, 472-4.7 kOhm, 112-1.1 kOhm, 106 - 10 MOhm, 2741 - 2.74 kOhm। कम प्रतिरोध वाले प्रतिरोधों के अंकन में "R" अक्षर होता है, उदाहरण के लिए, 4R7 - 4.7 ओम, 54R9 - 54.9 ओम।

चिप जंपर्स, जिसका प्रतिरोध 0.05 ओम से अधिक नहीं होना चाहिए, को 000 चिह्नित किया गया है।

कैपेसिटर आमतौर पर पैकेजिंग कंटेनर पर अंकित होते हैं। क्षमता के लिए प्रतीक: पहले दो अंक पिकोफराड में नाममात्र मूल्य को दर्शाते हैं, तीसरा अंक दाईं ओर जोड़े गए शून्य की संख्या को इंगित करता है। उदाहरण के लिए: 105 - 1 µF, 153 - 0.015 µF.

पर्याप्त रूप से बड़े सतह क्षेत्र वाले इलेक्ट्रोलाइटिक कैपेसिटर में ऑपरेटिंग वोल्टेज और कैपेसिटेंस मान का एक कोडित पदनाम हो सकता है। कई एन्कोडिंग विकल्प संभव हैं:

a) कोड में दो या तीन अक्षर (अक्षर या संख्या) होते हैं। अक्षर वोल्टेज और कैपेसिटेंस को दर्शाते हैं, और संख्या गुणक को इंगित करती है

अक्षरों के पहले ऑपरेटिंग वोल्टेज की सीमा को दर्शाने वाली संख्या हो सकती है:

बी) कोड में चार अक्षर (अक्षर और संख्या) होते हैं जो रेटेड क्षमता और ऑपरेटिंग वोल्टेज को दर्शाते हैं। पहला अक्षर वोल्टेज को दर्शाता है, अगले दो अंक पीएफ में कैपेसिटेंस को दर्शाते हैं, और अंतिम अंक शून्य की संख्या को दर्शाता है। उदाहरण के लिए: E475 25 V तक के ऑपरेटिंग वोल्टेज के साथ 4.7 μF की क्षमता वाला एक संधारित्र है। कभी-कभी कैपेसिटेंस को अक्षर c का उपयोग करके इंगित किया जा सकता है: E4ts7 उपरोक्त उदाहरण के अनुरूप संधारित्र का पदनाम है।

सामान्य तौर पर, एक चिप घटक को आयाम एल (लंबाई), बी (चौड़ाई), एच (ऊंचाई), डी या / (पैड चौड़ाई) द्वारा चित्रित किया जा सकता है जैसा कि चित्र 2.3 में दिखाया गया है। चिप रेसिस्टर्स का आकार बिजली अपव्यय पर निर्भर करता है, और चिप कैपेसिटर का आकार नाममात्र कैपेसिटेंस और ऑपरेटिंग वोल्टेज पर निर्भर करता है।

आवासों का आकार और आयाम अंतरराष्ट्रीय और राष्ट्रीय मानकों (IEC115, IEC384) द्वारा मानकीकृत हैं। ये मानक केएमपी के डिजाइन के लिए दो जोड़ी संख्याओं के रूप में एक पदनाम प्रणाली का उपयोग करते हैं जो एक इंच के सौवें हिस्से में आवास की लंबाई और चौड़ाई को दर्शाते हैं (आकार 0101 (0.25x0.25 मिमी) से 2225 (5.7x6) तक .3 मिमी)। कुछ के तुलनात्मक आकार 1.27 मिमी ग्रिड की पृष्ठभूमि के खिलाफ माचिस की तीली की तुलना में प्रतिरोधों के आकार चित्र 2.4 में दिखाए गए हैं।

कुछ कंपनियाँ केस के मानक आकार का पदनाम मिमी में देती हैं: 1005 - (1.0x0.5) मिमी, जो केस के उपरोक्त पदनाम 0402 से मेल खाता है; 3216 - (3.2x1.6) मिमी - पदनाम 1206 से मेल खाता है।

घरेलू उद्योग सामान्य उपयोग के लिए चिप रेसिस्टर्स R1-12, प्रिसिजन रेसिस्टर्स R1-16, रेसिस्टर्स के सेट HP1-29, चिप जंपर्स P1-23 का उत्पादन करता है। जम्पर चिप्स का उपयोग टोपोलॉजी डिज़ाइन के दौरान तारों में संक्रमण प्रदान करने के लिए किया जाता है। वे 3.2x1.6x0.6 मिमी (1206) के समग्र आयामों के साथ निर्मित होते हैं और उनका प्रतिरोध 0.05 ओम से अधिक नहीं होता है।

सतह पर लगाने के लिए चिप कैपेसिटर को मल्टीलेयर सिरेमिक कैपेसिटर (K10-9M, K10-17-4v, K10-42, K10-43, K10-47, K10-50v, K10-56, K10-57, K10-60v) द्वारा दर्शाया जाता है। K10 -69, K10-73-6v), टैंटलम ऑक्साइड सेमीकंडक्टर (K53-25, K53-36, K53-37) और एल्यूमीनियम ऑक्साइड सेमीकंडक्टर K53-40।

एमईएलएफ आवास(मेटल इलेक्ट्रोड फेस बॉन्डेड) - एक बेलनाकार शरीर जिसमें धातुयुक्त सिरों के रूप में अंतर्निर्मित इलेक्ट्रोड होते हैं (चित्र 2.5)। डायोड, रेसिस्टर्स, कैपेसिटर, इंडक्टर्स के लिए डिज़ाइन किया गया। केस का व्यास 1.25 मिमी से 2.2 मिमी, लंबाई - 2 से 5.9 मिमी तक है।

एमईएलएफ आवास की लागत कम है, लेकिन इसकी स्थापना कठिन है। टीएमपी के विकास की शुरुआत में यह जापान में व्यापक हो गया। ऐसे पैकेजों में घरेलू घटकों के उदाहरण प्रतिरोधक पीएल-11, पी1-30 हैं।

छोटा डायोड एसओडी पैकेज(छोटी रूपरेखा डायोड) - दो गल-विंग टर्मिनलों वाला एक प्लास्टिक केस (चित्र 2.6)। डायोड, एलईडी, वैरिकैप के लिए डिज़ाइन किया गया। सबसे आम SOD-80 हाउसिंग है, जिसका घरेलू एनालॉग GOST 18472-88 के अनुसार KD-34 हाउसिंग है।

चित्र 2.5 - एमईएलएफ प्रकार का आवास चित्र 2.6 - एसओडी प्रकार का आवास

छोटा एसओटी ट्रांजिस्टर पैकेज(स्मॉल आउटलाइन ट्रांजिस्टर) में 3 से 6 आउटपुट होते हैं (चित्र 2.7)।

चित्र 2.7 - एसओटी प्रकार के बाड़े

केस में एक प्लास्टिक का खोल और छोटे गल-विंग प्रकार के लीड हैं। इसमें ट्रांजिस्टर के अलावा डायोड, वैरिकैप और एम्प्लीफायर लगाए जा सकते हैं। यह पहला सरफेस माउंट पैकेज है जिसका विकास कार्यक्रम 25 साल से भी पहले सीमेंस द्वारा लागू किया गया था। सबसे आम SOT-23 पैकेज का आयाम 2.9x1.3x1.1 मिमी है।

इस प्रकार के आवास के आगे के विकास एसओटी-89, एसओटी-143, एस-मिनी, एसएस-मिनी हैं। बाद के विकासों में पिनों के बीच की दूरी को 0.65 -0.5 मिमी तक कम करना शामिल है, जिससे केस के आयाम को 1.6x1.6x0.75 मिमी तक कम करना संभव हो गया। इस प्रकार के घरेलू मामलों को KT-46 (SOT-23), KT-47 (SOT-89), KT-48 (SOT-143) मामलों द्वारा दर्शाया जाता है। आवासों के मुख्य ज्यामितीय आयाम चित्र 2.8 में दिखाए गए हैं।

एसओटी-23 (केटी-46)

एसओटी-89 (केटी-47)

एसओटी-89 (केटी-47)

चित्र 2.8 - एसओटी प्रकार के बाड़ों के समग्र आयाम

माइक्रो सर्किट के लिए छोटे आकार के पैकेज लीड के आकार (गल-विंग, जे-आकार का लीड), आवास के दो या चार किनारों पर उनका स्थान, और आवास की सामग्री (प्लास्टिक या सिरेमिक) के आधार पर कई समूहों में जोड़ा जा सकता है:

- आवास का प्रकारSOIC (छोटी रूपरेखा एकीकृत सर्किट) यू शराबी (छोटे आउटलाइन पैकेज) गल विंग के आकार में दो तरफा पिनआउट के साथ (चित्र 2.9ए, 2.9.6)। इस प्रकार के केस के लिए पिन स्पेसिंग 1.27 मिमी है, पिनों की संख्या 6 से 42 तक है। इस प्रकार के केस का एक और विकास केस का निर्माण था एसएसओआईसी (छोटी आउटलाइन इंटीग्रेटेड सर्किट को सिकोड़ें) पिन के बीच की दूरी को घटाकर 0.635 मिमी और अधिकतम संख्या 64 (चित्रा 2.9 सी) और आवास के साथ टीएसओपी (पतले छोटे आउटलाइन पैकेज) जिसमें शरीर की ऊंचाई घटाकर 1.27 मिमी (चित्र 2.8डी) और पिनों के बीच की दूरी घटाकर 0.3 - 0.4 मिमी कर दी गई;

- आवास का प्रकारSOJ ("जे" लीड के साथ छोटी रूपरेखा) जे-आकार के लीड की दो तरफा व्यवस्था के साथ, आवास के नीचे मुड़ी हुई (चित्र 2.10)। पिनों की पिच 1.27 मिमी है, उनकी कुल संख्या 14 से 28 तक है।

चित्र 2.9 - गल विंग के आकार में दो तरफा पिनआउट वाले विभिन्न प्रकार के माइक्रोसर्किट पैकेज: ए-एसओआईसी प्रकार का पैकेज; बी-बॉडी टाइप एसओपी; सी - एसएसओआईसी प्रकार का आवास; जी - टीएसओपी प्रकार का आवास

चित्र 2.10 - जे-आकार के लीड के साथ माइक्रोक्रिकिट केस: ए - केस का सामान्य दृश्य; बी - टर्मिनल डिजाइन

- आवास का प्रकारक्यूएफपी (क्वाड फ्लैट पैक) और एसक्यूएफपी (श्रिंक क्वाड फ़्लैट पैक), जिसमें "गल विंग" के आकार का लीड होता है, जो चार तरफ समान रूप से वितरित होता है (चित्र 2.11 ए)। एक प्रकार का आयताकार आकार का केस भी होता है - SQFP-R (चित्र 2.11 b)। पिनों की पिच काफी छोटी है - केवल 0.3 - 0.5 मिमी, जो आपको 440 तक पिनों की कुल संख्या के साथ केस बनाने की अनुमति देती है;

चित्र 2.11 - गल विंग के आकार में चार-तरफा पिनआउट वाले विभिन्न प्रकार के माइक्रोसर्किट पैकेज: ए - क्यूएफपी और एसक्यूएफपी पैकेज; बी-केस प्रकार SQFP-R

- आवास का प्रकारपीएलसीसी (प्लास्टिक लीडेड चिप कैरियर) - जे-लीड के साथ एक वर्गाकार प्लास्टिक क्रिस्टल कैरियर (चित्र 2.12ए) और प्रकारपीएलसीसी- आर (प्लास्टिक लीडेड चिप कैरियर आयताकार) - जे-लीड के साथ एक आयताकार प्लास्टिक क्रिस्टल कैरियर (चित्र 2.126)। इस प्रकार के मामलों में आधुनिक मानकों के अनुसार महत्वपूर्ण पिन रिक्ति होती है - 1.27 मिमी और, इसलिए, बड़े ज्यामितीय आयाम। एक वर्गाकार केस के लिए पिनों की संख्या 20 से 124 तक है, एक आयताकार केस के लिए - 18 से 32 तक;

चित्र 2.12 - जे-आकार के लीड के साथ आईसी केस

और चार-तरफा पिन व्यवस्था:

ए-स्क्वायर पीएलसीसी; बी-आयताकार पीएलसीसी-आर

- एलसीसीसी आवास(सीसा रहित सिरेमिक चिप कैरियर) - सीसा रहित सिरेमिक क्रिस्टल वाहक (चित्र 2.13)। ऐसे मामले की साइड सतहों पर 1.27 मिमी की वृद्धि में स्थित विशेष धातुयुक्त अवकाश होते हैं, जो असेंबली को डोज़्ड सोल्डर के साथ टांका लगाने पर बोर्ड के संपर्क पैड के साथ विद्युत कनेक्शन बनाने का काम करते हैं।

चित्र 2.13- एलसीसीसी आवास

SOIC प्रकार के बाड़ों का घरेलू एनालॉग GOST 17467-88 के अनुसार उपप्रकार 43 बाड़े हैं। इन आवासों के आयामी चित्र और आयाम चित्र 2.14 और तालिका 2.1 में दिखाए गए हैं।

चित्र 2.14 - उपप्रकार 43 आवासों के समग्र आयाम

तालिका 2.1 - 43 वी उपप्रकार आवासों के समग्र आयाम मिलीमीटर

|

आकार कोड |

पिनों की संख्या |

||||

QFP प्रकार के आवासों का घरेलू एनालॉग GOST 17467-88 के अनुसार उपप्रकार 44 आवास हैं। इन आवासों के आयामी चित्र और आयाम चित्र 2.15 और तालिका 2.2 में दिखाए गए हैं।

वैश्विक इलेक्ट्रॉनिक्स उद्योग सभी टीएमपी आईसी का लगभग 90% प्लास्टिक मामलों में और केवल 10% सिरेमिक मामलों में उत्पादन करता है। सिरेमिक मामलों में काफी उच्च प्रदर्शन संकेतक होते हैं। इस प्रकार, सिरेमिक मामलों में माइक्रोसर्किट की ऑपरेटिंग तापमान सीमा -55 से +125°C तक है, और प्लास्टिक के मामलों में - -10 से +85°C तक है। हालांकि, सिरेमिक मामलों का वजन और लागत बहुत अधिक होती है, इसलिए उनका उपयोग, एक नियम के रूप में, सबसे महत्वपूर्ण मामलों में किया जाता है।

चित्र 2.15 - उपप्रकार 44 आवासों के समग्र आयाम

तालिका 2.2 - उपप्रकार 44 आवासों के समग्र आयाम

|

आकार कोड |

पिनों की संख्या |

|||||

स्विच, फ़्यूज़, इंडक्टर्स, इलेक्ट्रोलाइटिक कैपेसिटर और वेरिएबल रेसिस्टर्स जैसे अनियमित आकार के घटकों के लिए गैर-मानक आवास चित्र 2.16 में दिखाए गए हैं।

चित्र 2.16 - आईएलसी के लिए गैर-मानक आवास

घरेलू उद्योग निम्नलिखित प्रकार के टीएमपी संस्करण में ट्यूनिंग रेसिस्टर्स का उत्पादन करता है: आरपी1-75, आरपी1-82, आरपी1-83, आरपी1-98। प्रतिरोधों की प्रतिरोध सीमा 10 ओम से 3.3 MOhms तक होती है, जिससे 0.25 W की बिजली अपव्यय की अनुमति मिलती है। कुल आयाम 4.5x4.5x3.5 मिमी से अधिक नहीं है।

आज मानव जीवन के ऐसे क्षेत्र का नाम बताना मुश्किल है जहां एकीकृत सर्किट का उपयोग नहीं किया जाता है: दूरसंचार, ऑटोमोटिव उद्योग, प्रक्रिया नियंत्रण प्रणाली, कंप्यूटर और घरेलू उपकरण, आदि। एकीकृत सर्किट का इतना व्यापक उपयोग उनकी डिज़ाइन सुविधाओं पर छाप छोड़ता है।

एकीकृत सर्किट पैकेजों की विविधता

आज, एकीकृत सर्किट दो संस्करणों में निर्मित होते हैं - पैकेज्ड और अनपैकेज्ड। पैकेज रहित चिप एक खुली चिप है जिसे हाइब्रिड चिप या माइक्रोअसेंबली में इंस्टॉलेशन के लिए डिज़ाइन किया गया है। बाहरी प्रभावों से बचाने के लिए, एकीकृत सर्किट को प्लास्टिक या सिरेमिक केस में रखा जाता है। माइक्रोचिप पैकेज मानकीकृत हैं। इंजीनियरों को अक्सर अंग्रेजी भाषा के दस्तावेज़ मिलते हैं जिनमें एकीकृत सर्किट के पैकेज को "चिप पैकेज", "चिप कंटेनर" या "चिप कैरियर" कहा जाता है।

थ्रू-होल माउंटिंग के लिए आयातित आईसी हाउसिंग

मुद्रित सर्किट बोर्ड छेद में लगाने के लिए डिज़ाइन किए गए आयातित एकीकृत सर्किट पैकेजों की सबसे आम श्रृंखला नीचे दी गई है।

यह केस आकार में आयताकार है जिसमें माइक्रोसर्किट को छेद में लगाने के लिए लंबे संकीर्ण किनारों पर पिन पिन की दो पंक्तियाँ हैं।

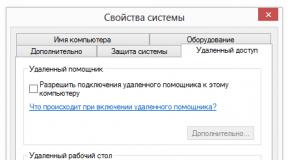

डीआईपी पैकेज हो सकता है:

- पीडीआईपी - शरीर प्लास्टिक (प्लास्टिक डीआईपी) से बना है;

- एसपीडीआईपी - संपीड़ित प्लास्टिक चिप हाउसिंग (सिकोड़ें प्लास्टिक डीआईपी);

- एसडीआईपी - पतला शरीर (स्किनी डीआईपी);

- CerDIP या CDIP - बॉडी सिरेमिक (सिरेमिक डीआईपी) से बनी है;

- एमडीआईपी - मोल्डेड चिप केस (मोल्डेड डुअल इन-लाइन पैकेज);

- एफडीआईपी - रिकॉर्डिंग के लिए एक खिड़की के साथ आवास (विंडो फ्रिट-सील डीआईपी);

- एचडीआईपी - हीट-डिसीपेटिंग हाउसिंग (हीट-डिसीपेटिंग डीआईपी)।

आवास पदनाम पिनों की संख्या को इंगित करता है: DIP8, DIP14, DIP16, आदि।

पीसीबी छेदों में ऊर्ध्वाधर स्थापना के लिए एक सपाट आयताकार आवास, जिसमें लंबी संकीर्ण तरफ पिन की एक पंक्ति होती है। आवास पदनाम पिनों की संख्या को इंगित करता है: SIP7, SIP8, SIP9, आदि। यह आवास एकीकृत सर्किट को मुद्रित सर्किट बोर्ड पर काफी कॉम्पैक्ट रूप से रखने की अनुमति देता है।

चेकरबोर्ड पैटर्न में दो पंक्तियों में ज़िगज़ैग पैटर्न में व्यवस्थित पिन पिन के साथ मुद्रित सर्किट बोर्ड छेद में लंबवत माउंटिंग के लिए फ्लैट आवास। इनमें आमतौर पर मेमोरी चिप्स होते हैं।

आयातित सतह माउंट एकीकृत सर्किट पैकेज

इलेक्ट्रॉनिक उपकरणों को असेंबल करते समय, सरफेस माउंटिंग तकनीक एसएमटी (सरफेस माउंट टेक्नोलॉजी) का अक्सर उपयोग किया जाता है। इलेक्ट्रॉनिक घटक जो सतह पर लगाने के लिए निर्मित किए जाते हैं उन्हें एसएमडी (सरफेस माउंटेड डिवाइस) घटक कहा जाता है। सतह पर लगाने के लिए डिज़ाइन किए गए आयातित एकीकृत सर्किट पैकेजों की सबसे आम श्रृंखला नीचे दी गई है।

एसओआईसी या एसओ (स्मॉल-आउटलाइन इंटीग्रेटेड सर्किट) चिप पैकेज, जिसे एसओपी (स्मॉल-आउटलाइन पैकेज) के रूप में भी जाना जाता है।

चिप पैकेज का आकार काफी पतला आयताकार है, जो डीआईपी पैकेज की याद दिलाता है, लेकिन इसे सतह पर लगाने के लिए डिज़ाइन किया गया है। बाहर की ओर घुमावदार लीड दो लंबे किनारों पर स्थित हैं और पीसीबी के उसी तरफ सोल्डर किए गए हैं जहां आवास स्थित है। आवास पदनाम पिनों की संख्या को इंगित करता है।

- एसएसओपी - संपीड़ित छोटे आकार के चिप पैकेज (सिकोड़ें एसओपी);

- टीएसओपी - पतला छोटे आकार का पैकेज (पतला एसओपी);

- टीएसएसओपी - अल्ट्रा-थिन चिप पैकेज (थिन श्रिंक एसओपी);

- क्यूएसओपी - वर्गाकार निकाय (क्वार्टर एसओपी);

- एमएसओपी - कम आकार का एसओपी हाउसिंग (मिनी एसओपी);

- सीएसओपी - सिरेमिक चिप पैकेज (सिरेमिक एसओपी);

- एचएसओपी - हीट सिंक के साथ बॉडी (हीट सिंक एसओपी);

- एचएसएसओपी - हीट सिंक (हीट सिंक श्रिंक एसओपी) के साथ छोटे आकार का आवास;

- HTSSOP - हीट सिंक (हीट सिंक थिन श्रिंक एसओपी) के साथ पतला चिप पैकेज;

- वीएसओपी - लघु केस (बहुत छोटा आउटलाइन पैकेज);

- क्यूएसओपी - चौकोर आकार का केस (क्वार्टर साइज एसओपी)।

एक चौकोर, सपाट माइक्रोक्रिकिट बॉडी जिसके संकीर्ण किनारों पर पिन की चार पंक्तियाँ हैं, वे बाहर की ओर मुड़ी हुई हैं।

इस मामले के अन्य रूप भी हैं:

- टीक्यूएफपी - पतला चिप पैकेज (पतला क्यूएफपी);

- एलक्यूएफपी - लो-प्रोफाइल चिप पैकेज (लो-प्रोफाइल क्यूएफपी);

- एसक्यूएफपी - संपीड़ित क्यूएफपी पैकेज (सिकोड़ें क्यूएफपी);

- वीटीक्यूएफपी - अल्ट्रा थिन केस (वेरी थिन क्यूएफपी);

- HQFP - हीट सिंक (हीट सिंक QFP) के साथ चिप पैकेज।

निम्न प्रोफ़ाइल, निचले संपर्कों के साथ वर्गाकार सिरेमिक आवास, सतह पर लगाने के लिए डिज़ाइन किया गया। आवास पदनाम संपर्कों की संख्या को इंगित करता है, उदाहरण के लिए: LCC16, LCC32, आदि।

इस लेख में, आपकी जानकारी के लिए, हमने विस्तृत चित्रों के बिना आयातित माइक्रो-सर्किट के केवल कुछ मामले उपलब्ध कराए हैं।

ध्यान!माइक्रो-सर्किट ऑर्डर करते और खरीदते समय, आपको केस के प्रकार पर ध्यान देने की आवश्यकता है, क्योंकि निर्माता अक्सर विभिन्न प्रकार के मामलों में एक ही माइक्रो-सर्किट का उत्पादन करते हैं।

मैक्सिम शाकोलिन

डीडीपीएके |

डुबोना |

डीपीएके |

एफडीआईपी |

पीडीआईपी |

पेंटावाट |

पीएलसीसी |

क्यूडीआईपी |

क्यूएफपी |

एसआईपी |

इसलिए |

SO8 |

SOT23 |

SOT103 |

SOT223 |

एसक्यूएल |

एस.क्यू.पी. |

एस.डब्ल्यू. |

T7-TO220 |

TO3 |

TO5 |

TO50 |

TO52 |

TO92 |

TO99 |

TO100 |

TO220 |

TO220-5 |

TO220ISO |

TO252 |

TO263 |

TO263 |

TO268 |

टीएसओपी |

ज़िप |

जोड़ना:

डुबोना

डुबोना(डुअल इनलाइन पैकेज) - संपर्कों की दो पंक्तियों वाला एक आवास। यह एक आयताकार मामला है जिसके संपर्क लंबे किनारों पर स्थित हैं। आवास सामग्री के आधार पर, दो संस्करण हैं:

पीडीआईपी(प्लास्टिक डीआईपी) - एक प्लास्टिक बॉडी है;

सीडीआईपी(सिरेमिक डीआईपी) - एक सिरेमिक बॉडी है;

CDIP-40 पैकेज में प्रोसेसर PDIP-40 पैकेज में प्रोसेसर क्यूएफपी

क्यूएफपी(क्वाड फ्लैट पैकेज) - संपर्कों की चार पंक्तियों वाला एक फ्लैट पैकेज। यह एक चौकोर केस है जिसके संपर्क किनारों पर स्थित हैं। आवास सामग्री के आधार पर, दो संस्करण हैं:

पीक्यूएफपी(प्लास्टिक क्यूएफपी) - एक प्लास्टिक बॉडी है;

सीक्यूएफपी(सिरेमिक क्यूएफपी) - एक सिरेमिक बॉडी है;

अन्य विकल्प भी हैं: टीक्यूएफपी(पतला क्यूएफपी) - कम शरीर की ऊंचाई के साथ, एलक्यूएफपी(लो-प्रोफाइल क्यूएफपी) और कई अन्य।TQFP-304 पैकेज में प्रोसेसर

पीएलसीसी/सीएलसीसी

पीएलसीसी(प्लास्टिक लीडेड चिप कैरियर) और सीएलसीसी(सिरेमिक लीडेड चिप कैरियर) किनारों के साथ स्थित संपर्कों के साथ एक वर्गाकार आवास है, जिसे एक विशेष पैनल (अक्सर "पालना" कहा जाता है) में स्थापित करने के लिए डिज़ाइन किया गया है। वर्तमान में, पीएलसीसी पैकेज में फ्लैश मेमोरी चिप्स का व्यापक रूप से मदरबोर्ड पर BIOS चिप्स के रूप में उपयोग किया जाता है।

एल सी सी

एल सी सी(लीडलेस चिप कैरियर) एक लो-प्रोफाइल, वर्गाकार सिरेमिक पैकेज है जिसके नीचे संपर्क स्थित हैं, जो सतह पर लगाने के लिए डिज़ाइन किया गया है।PLCC-68 पैकेज में प्रोसेसर

पी.जी.ए.

पी.जी.ए.(पिन ग्रिड ऐरे) - पिन मैट्रिक्स वाला एक आवास। यह एक वर्गाकार या आयताकार आवास है जिसके नीचे पिन संपर्क स्थित हैं। आधुनिक प्रोसेसर में, पिन को चेकरबोर्ड पैटर्न में व्यवस्थित किया जाता है। आवास सामग्री के आधार पर, तीन संस्करण हैं: पीपीजीए(प्लास्टिक पीजीए) - एक प्लास्टिक बॉडी है; सीपीजीए(सिरेमिक पीजीए) - एक सिरेमिक बॉडी है; ओपीजीए(ऑर्गेनिक पीजीए) - कार्बनिक पदार्थ से बना शरीर है;

पीजीए पैकेज में निम्नलिखित संशोधन हैं:

एफसीपीजीए(फ्लिप-चिप पीजीए) - इस मामले में, खुली प्रोसेसर चिप केस के शीर्ष पर स्थित होती है।

FCPGA2(फ्लिप-चिप पीजीए 2) - प्रोसेसर चिप को कवर करने वाले हीट स्प्रेडर की उपस्थिति से एफसीपीजीए से भिन्न होता है।

एमएफसीपीजीए(माइक्रो फ्लिप-चिप पीजीए) - एफसीजीए पैकेज का एक कॉम्पैक्ट संस्करण।

एमपीजीए(माइक्रो पीजीए) - FCPGA2 पैकेज का एक कॉम्पैक्ट संस्करण।

संक्षिप्त नाम SPGA (स्टैगर्ड पीजीए) का उपयोग कभी-कभी कंपित पिन वाले पैकेजों को संदर्भित करने के लिए किया जाता है।

सीपीजीए पैकेज में प्रोसेसर FCPGA पैकेज में प्रोसेसर FCPGA2 पैकेज में प्रोसेसर बीजीए

बीजीए(बॉल ग्रिड ऐरे) - एक पीजीए पैकेज है जिसमें पिन संपर्कों को सोल्डर गेंदों से बदल दिया जाता है। सतह पर लगाने के लिए डिज़ाइन किया गया। इसका उपयोग अक्सर मोबाइल प्रोसेसर, चिपसेट और आधुनिक जीपीयू में किया जाता है। निम्नलिखित BGA पैकेज विकल्प उपलब्ध हैं:

एफसीबीजीए(फ्लिप-चिप बीजीए) - इस पैकेज में, ओपन प्रोसेसर चिप पैकेज के शीर्ष पर स्थित है, जो कार्बनिक सामग्री से बना है।

एमबीजीए(माइक्रो बीजीए) और एमएफसीबीजीए (माइक्रो फ्लिप-चिप बीजीए) कॉम्पैक्ट हाउसिंग विकल्प हैं।

एचएसबीजीएएलजीए

एलजीए(लैंड ग्रिड ऐरे) - एक पीजीए पैकेज है जिसमें पिन संपर्कों को पैड से बदल दिया जाता है। इसे स्प्रिंग संपर्कों के साथ एक विशेष सॉकेट में स्थापित किया जा सकता है, या मुद्रित सर्किट बोर्ड पर स्थापित किया जा सकता है। आवास सामग्री के आधार पर, दो संस्करण हैं: सीएलजीए(सिरेमिक एलजीए) - एक सिरेमिक बॉडी है; पीएलजीए(प्लास्टिक एलजीए) - एक प्लास्टिक बॉडी है; ओल्गा(ऑर्गेनिक एलजीए) - कार्बनिक पदार्थ से बनी बॉडी है; हीट स्प्रेडर के साथ OLGA हाउसिंग का एक कॉम्पैक्ट संस्करण है, जिसे FCLGA4 नामित किया गया है।

FCLGA4 पैकेज में प्रोसेसर